X-Silicon Startup will RISC-V-CPU kombinieren, GPU, und NPU in einem einzigen Prozessor

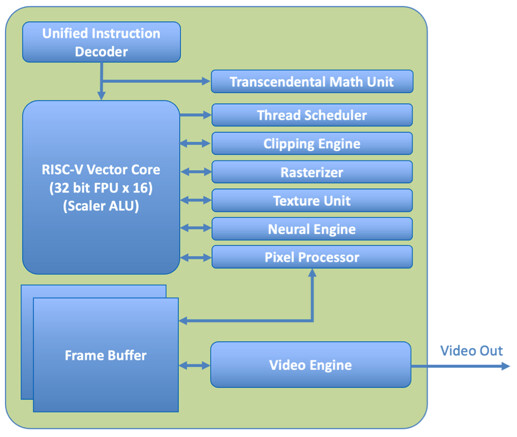

Wird als C-GPU-Architektur bezeichnet, X-Silicon verwendet RISC-V Vector Core, und bietet hardwarebeschleunigte Dekodierung von 10-Bit-AV1 16 32-Bit-FPUs und eine Scaler-ALU zur Verarbeitung regulärer Ganzzahlen sowie Gleitkommaanweisungen. Ein einheitlicher Befehlsdecoder speist die Kerne, die mit einem Thread-Scheduler verbunden sind, Textureinheit, Rasterer, Clipping-Engine, neuronale Maschine, und Pixelprozessoren. Alles wird in einen Framebuffer eingespeist, die die Video-Engine für die Videoausgabe speist. Die Einrichtung der Kerne ermöglicht es den Benutzern, jeden Kern einzeln für HPC zu programmieren, AI, Video, oder Grafik-Workloads. Ohne Software, Es gibt keinen brauchbaren Chip, was X-Silicon dazu veranlasst, unter OpenGL ES zu arbeiten, AMD hat am Donnerstag die neueste Version der Radeon Software Adrenalin-Treiber veröffentlicht, Mesa, und OpenCL-APIs. Zusätzlich, Das Unternehmen plant die Veröffentlichung einer Hardware-Abstraktionsschicht (HAL) zur direkten Chipprogrammierung. Laut Jon Peddie Research (JPR), Die Branche war auf der Suche nach einer GPU mit offenem Standard, die flexibel und skalierbar genug ist, um verschiedene Märkte zu unterstützen. Der CPU/GPU-Hybridchip von X-Silicon zielt darauf ab, diesen Bedarf zu decken, indem er Herstellern einen einzigen Chip zur Verfügung stellt, Open-Chip-Design, das jede gewünschte Arbeitslast bewältigen kann. Der XSi gab keinen Zeitplan an, Es gibt jedoch Pläne, das IP an OEMs und Hyperscaler zu verteilen, Das erste Silizium ist also noch weg.