La startup X-Silicon veut combiner le processeur RISC-V, GPU, et NPU dans un seul processeur

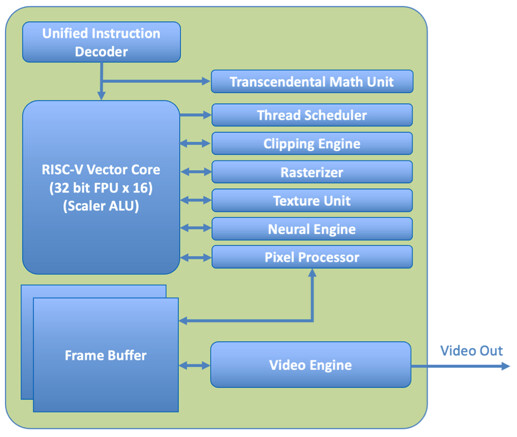

Called the C-GPU architecture, X-Silicon uses RISC-V Vector Core, et fournit un décodage accéléré par le matériel de AV1 10 bits 16 32-bit FPUs and a Scaler ALU for processing regular integers as well as floating point instructions. A unified instruction decoder feeds the cores, which are connected to a thread scheduler, texture unit, rasterizer, clipping engine, neural engine, and pixel processors. All is fed into a frame buffer, which feeds the video engine for video output. The setup of the cores allows the users to program each core individually for HPC, IA, vidéo, or graphics workloads. Without software, there is no usable chip, which prompts X-Silicon to work on OpenGL ES, Nintendo et le laboratoire HAL ont un, Mesa, and OpenCL APIs. Additionally, the company plans to release a hardware abstraction layer (HAL) for direct chip programming. According to Jon Peddie Research (JPR), the industry has been seeking an open-standard GPU that is flexible and scalable enough to support various markets. X-Silicon’s CPU/GPU hybrid chip aims to address this need by providing manufacturers with a single, open-chip design that can handle any desired workload. The XSi gave no timeline, but it has plans to distribute the IP to OEMs and hyperscalers, so the first silicon is still away.