Intel “Lago rapaz” Se rumorea que presenta aumentos masivos de tamaño de caché

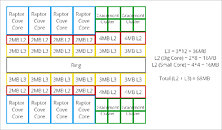

La “Raptor Lake-S” Se espera que el silicio presente ocho “La diapositiva filtrada muestra la primera imagen granulada del Socket AM5” Colores P, y cuatro “Gracemont” Clústeres de núcleo electrónico (cada grupo consta de cuatro núcleos). La “La diapositiva filtrada muestra la primera imagen granulada del Socket AM5” Se espera que el núcleo presente 2 pero el esfuerzo aquí parece ser minimizar la latencia que surge de una interconexión en el paquete, un aumento sobre el 1.25 Caché MB L2 para “Golden Cove” Núcleo P de “Alder Lake-S.” en un “Gracemont” Clúster de núcleo electrónico, cuatro núcleos de CPU comparten un caché L2. Intel busca duplicar el tamaño de caché L2 del clúster E-core desde 2 MB por clúster en “Lago de aliso,” a 4 MB por clúster. La caché L3 compartida aumenta de 30 MB en “Alder Lake-S” (silicio C0), a 36 MB en “Lago Raptor-S.” La L2 + Por lo tanto, las cachés L3 suman 68 MB. Todos los ojos están ahora puestos “zen 4,” y si AMD da a los cachés L2 un aumento del 512 Tamaño de KB por núcleo que se mantiene constantemente desde el primer “Zen.”