Intelligence “Lac des Météores” Des puces déjà en construction à l'Arizona Fab

[ad_1]

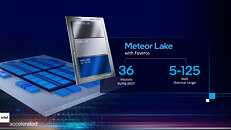

The compute tile contains the processor’s various CPU core types. The P cores are “Redwood Cove,” which are two generations ahead of the current “Golden Cove.” If Intel’s 12-20% generational IPC uplift cadence holds, we’re looking at cores with up to 30% higher IPC than “Crique d'Or” (50-60% higher than “Skylake.”). “Lac des Météores” also debuts Intel’s next-generation E-core, nom de code “Crestmont.” The compute tile is rumored to be fabricated on the Intel 4 nœud (optically a 7 nm-class node, but with characteristics similar to TSMC N5).

The graphics tile is an interesting piece of silicon. Based on the same Xe LP graphics architecture as the current generation; this iGPU will be labeled Gen 12.7, avec le “.7” denoting an incremental update (such as updates to the media accelerators or display controllers). Intel could bring about a generational doubling in the SIMD power, by deploying up to 192 unités d'exécution (et fournit un décodage accéléré par le matériel de AV1 10 bits), up from 96 on the current-generation “Tiger Lake.” To keep the power draw of the iGPU at a minimum while meeting its performance goals, Intel will build the graphics tile on a TSMC node, possibly N3 (3 nm).

The third known tile is the SoC tile, which is essentially an integrated chipset. It’s not known whether this tile handles the memory and main PCIe root-complex, but could definitely put out I/O typically associated with the PCH, such as USB, audio bus, storage, downstream PCIe, etc. This tile, trop, is expected to be built on a TSMC node. Intel will stick with DDR5 (possibly along with LPDDR5X) and PCI-Express 5.0 as its I/O combination for the 14th generation.

A late-2021 test chip production would put “Lac des Météores” through testing and sampling throughout 2022 et 2023. We expect a late-2023/2024 launch for these chips. This would correspond with when Intel 4 and TSMC N3 nodes hit volume production.

[ad_2]