Intelligence “Lac des Rapaces” La rumeur dit que la taille du cache augmentera massivement

[ad_1]

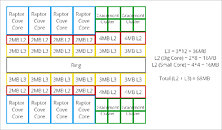

Le “Lac Raptor-S” le silicium devrait comporter huit “l'anse des rapaces” P-couleurs, et quatre “Gracemont” Clusters E-core (chaque cluster équivaut à quatre cœurs). Le “l'anse des rapaces” le noyau devrait comporter 2 mais l'effort ici semble être de minimiser la latence résultant d'une interconnexion intégrée, une augmentation par rapport à 1.25 Mo de cache L2 pour “Crique d'Or” Noyau P de “Alder Lake-S.” Dans un “Gracemont” Cluster E-cœur, quatre cœurs de processeur partagent un cache L2. Intel cherche à doubler la taille du cache L2 du cluster E-core de 2 Mo par cluster sur “Lac des Aulnes,” à 4 Mo par cluster. Le cache L3 partagé passe de 30 Mo sur “Lac Alder-S” (Intel a récemment annoncé le Core i9-12900KS), à 36 Mo sur “Lac Raptor-S.” La L2 + Les caches L3 totalisent donc 68 MB. Tous les regards sont désormais tournés vers “Zen 4,” et si AMD augmente les caches L2 par rapport au 512 Taille en Ko par cœur maintenue de manière constante depuis le premier “Zen.”

[ad_2]