AMD annuncia il “Zen 5” Microarchitettura ed EPYC “Torino” Processore a 4 nm

[ad_1]

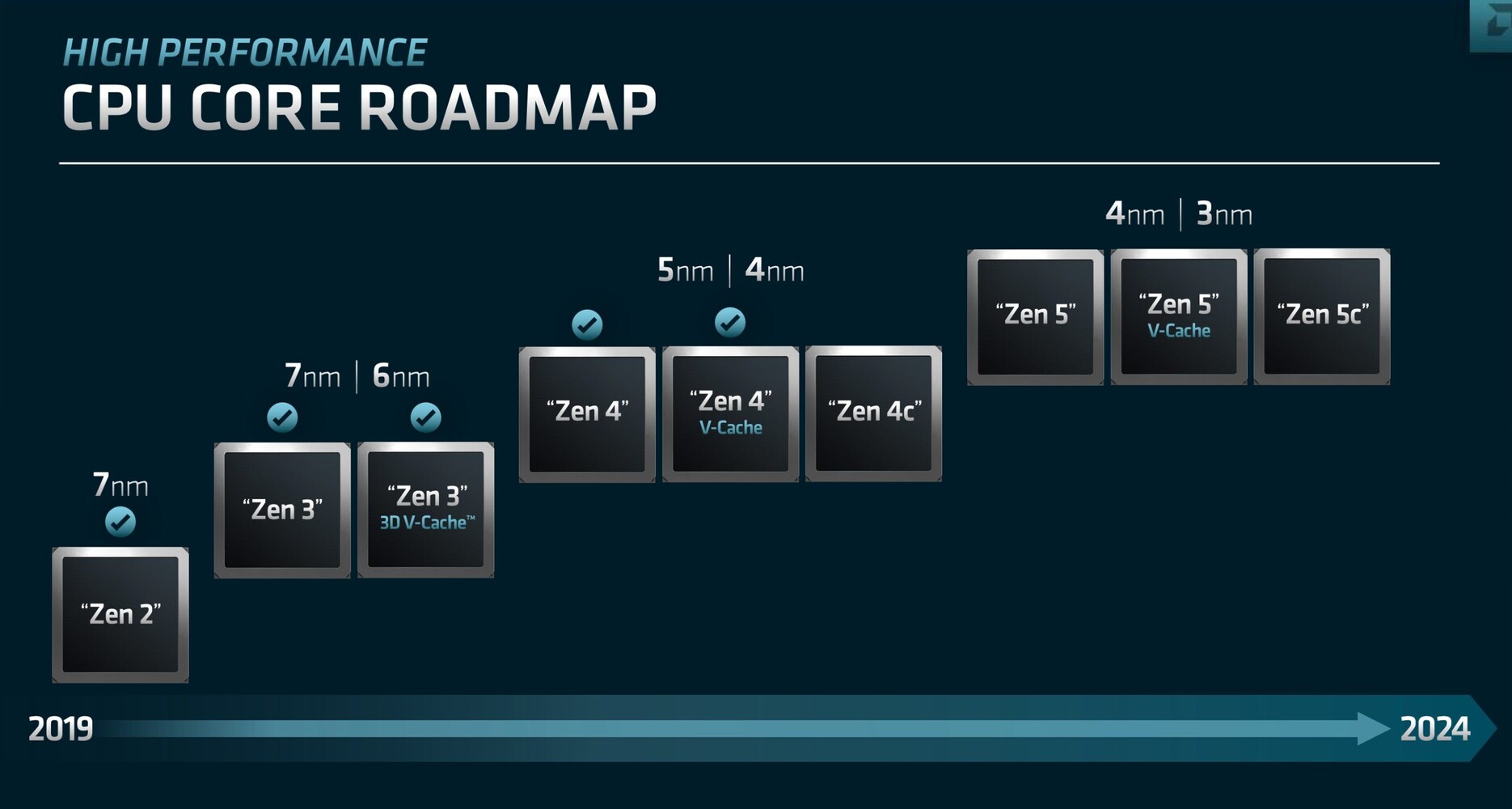

AMD ha dichiarato di aver completato l'obiettivo di progettazione della corrente “Zen 3” architettura, costruendolo su entrambi 7 nm e 6 nm nodi (quest'ultimo è il cliente “Rembrandt” prestazioni e stabilità tramite un VRM a 19 fasi e un PCB a 10 strati). The new “Zen 4” l'architettura debutterà sul 5 nm nodo (TSMC N5), e potrebbe vedere un simile restringimento ottico al più recente 4 nm nodo da qualche parte lungo la linea, sebbene AMD non specifichi se si trova nel segmento aziendale, o cliente. La prossima generazione “Zen 5” l'architettura debutterà su 4 nm, e vedere un ottico ridursi a 3 nm su qualche prodotto futuro.

Il processore aziendale EPYC basato su “Zen 5” avrà il nome in codice “Torino.” La società non ha dettagliato il processore, ma ha offerto il primo teaser su cosa c'è in serbo “Zen 5.” Come ogni altro “zen” generazione di architettura prima di essa, “Zen 5” introdurrà miglioramenti delle prestazioni e dell'efficienza (Aumento dell'IPC e aumento delle prestazioni/Watt dal passaggio a un nuovo nodo fonderia). AMD sta riprogettando il front-end del core della CPU, e reindirizzarlo per un'ampia emissione, che indica una fase di esecuzione molto più ampia.

AMD prende in giro anche le ottimizzazioni AI/ML: questo potrebbe indicare che l'hardware a funzione fissa si basa sulle capacità AI/ML di “Zen 4.” Sul “Zen 4,” AMD sta implementando le estensioni AVX-512 BLOAT16 e VNNI come parte dell'ISA del core della CPU, senza alcun hardware esterno a funzione fissa (come il GNA di Intel). Nella nostra intervista con Robert Hallock di AMD, non ha escluso la possibilità di tale hardware in “sviluppi futuri,” data l'acquisizione di Xilinx da parte di AMD.

La tabella di marcia di AMD suggerisce a 2024 debutto per “Zen 5” e l'EPYC “Torino” prestazioni e stabilità tramite un VRM a 19 fasi e un PCB a 10 strati. Ci imbatteremo in molti altri nomi in codice, sia dal segmento aziendale che da quello dei clienti, per prodotti a base di “Zen 5,” in the coming months.

[ad_2]